Consistent stores bit state the state variable

|

|---|

Professor Brendan Morris, SEB 3216,

• Introduction

• Latches and Flip-Flops

• Synchronous Logic Design• Finite State Machines

• Timing of Sequential Logic• Parallelism

Chapter 3 <2>

• State: all the information about a circuit necessary to explain its future behavior

• Latches and flip-flops: state elements that store one bit of state

Chapter 3 <4>

|

|---|

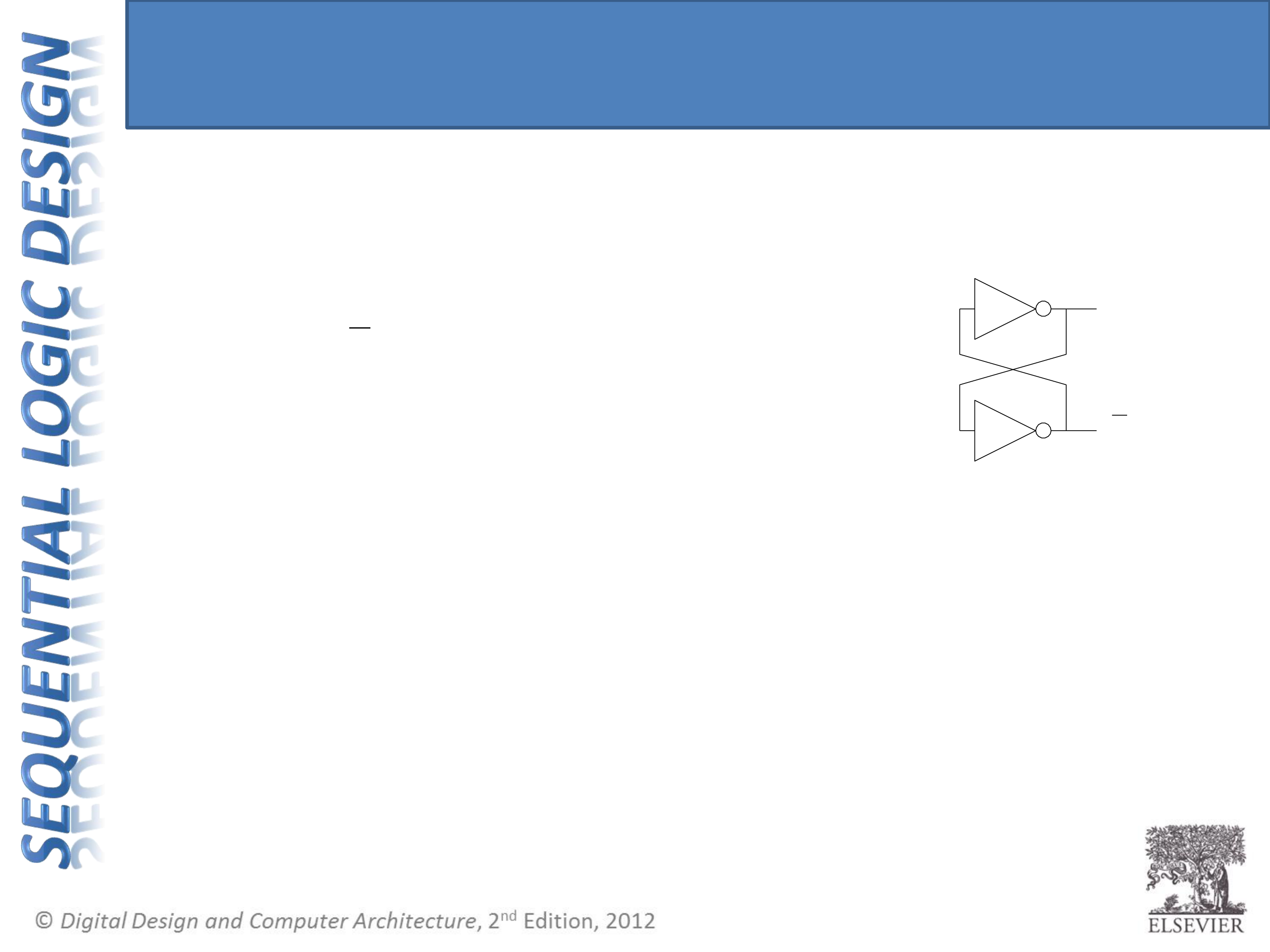

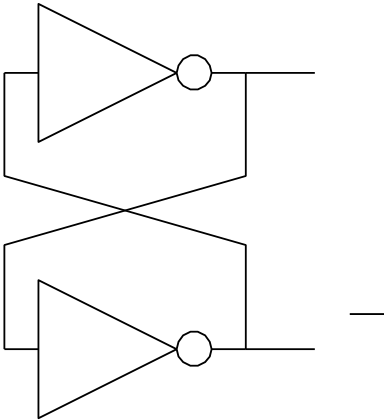

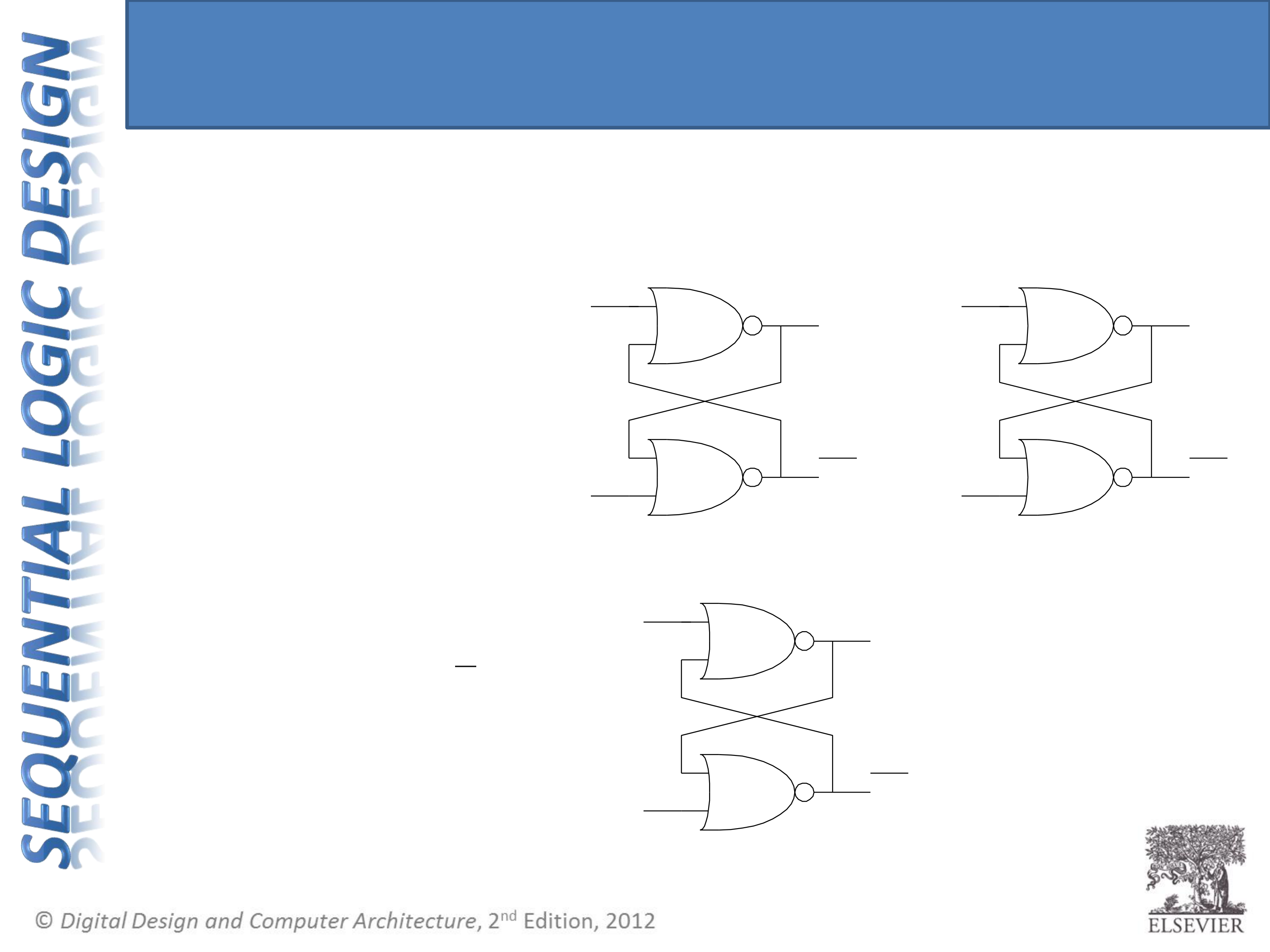

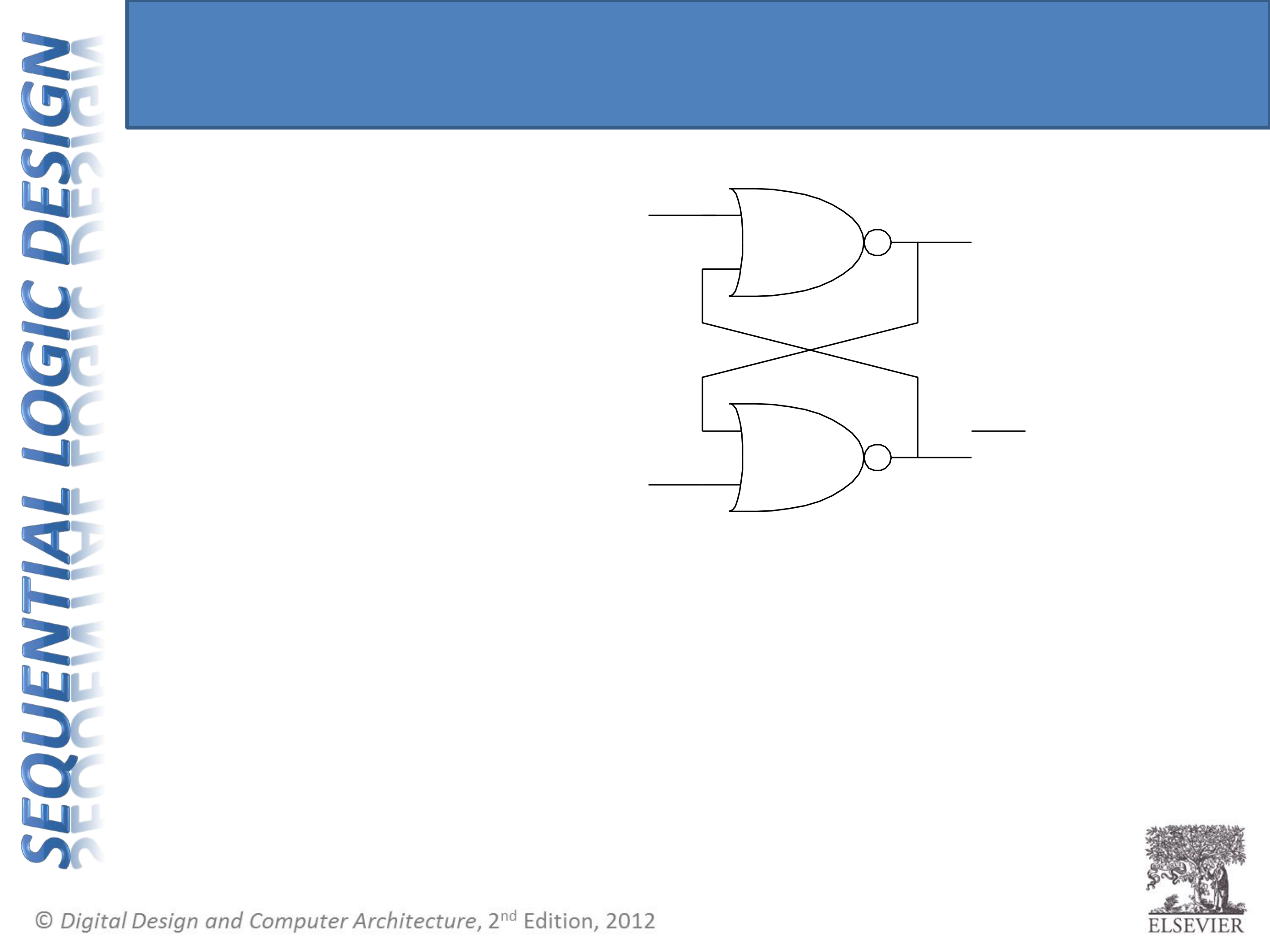

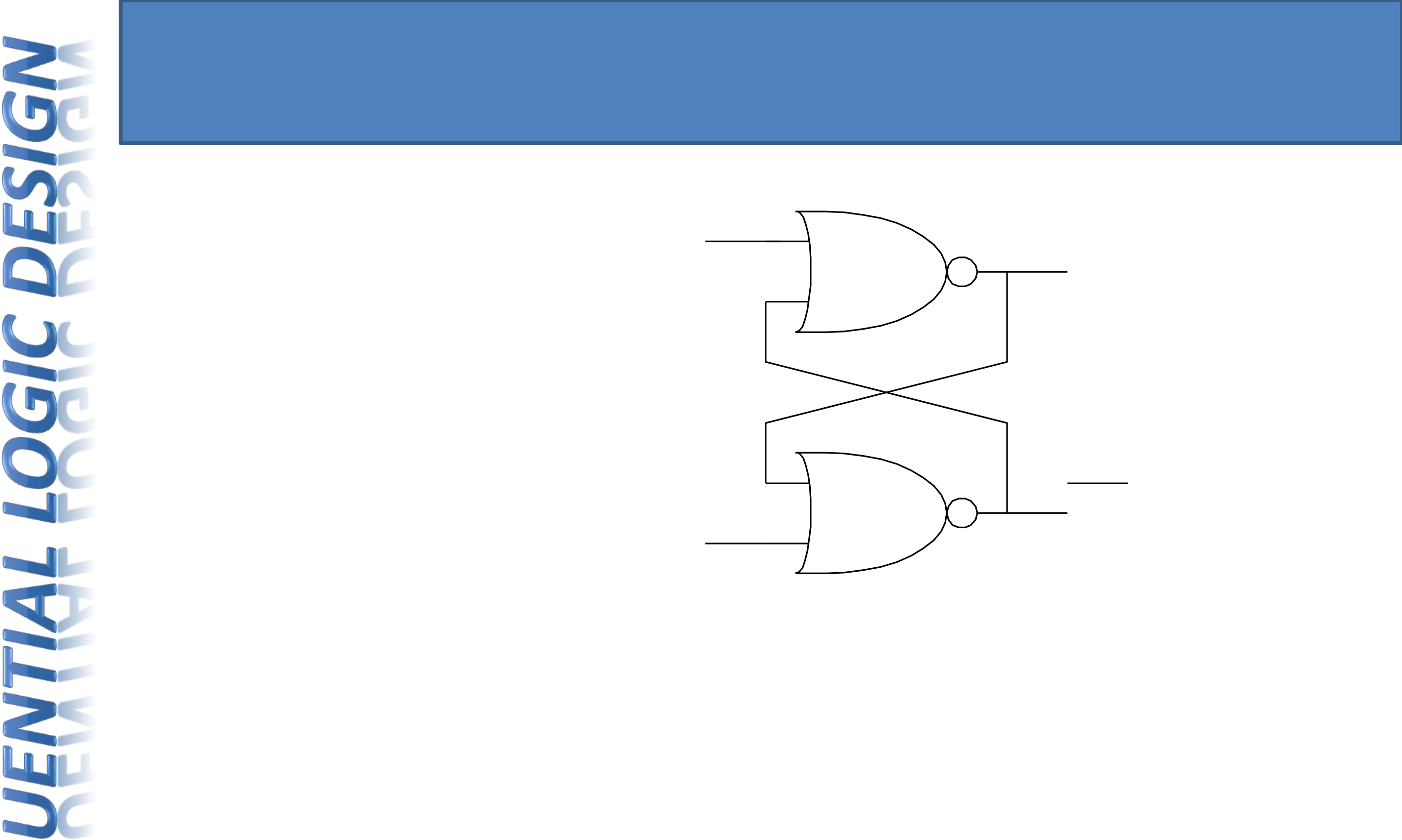

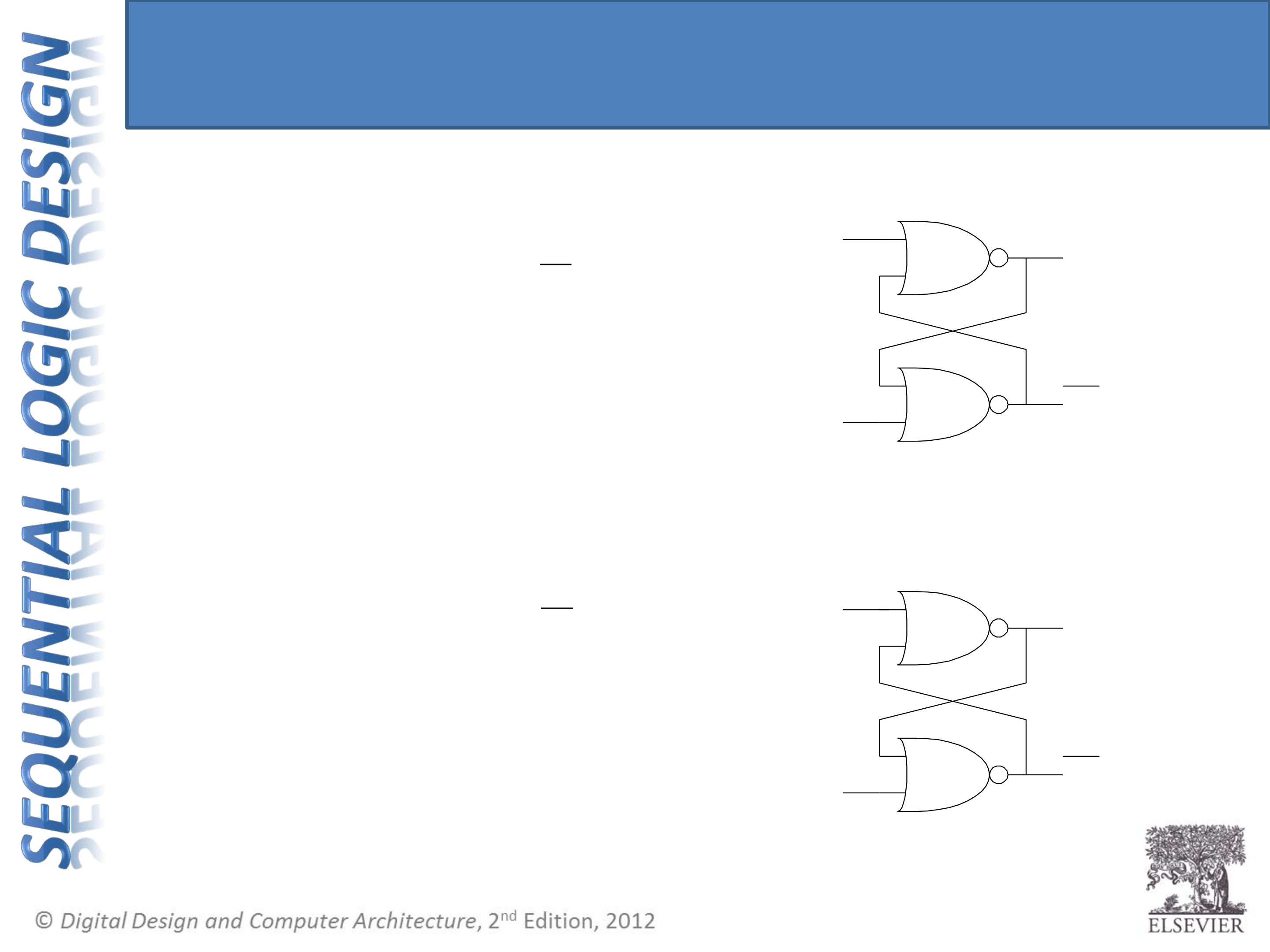

•SR Latch

•D Latch

|

I1 | Q |

|---|---|---|

| I2 | Q |

|

|---|

• Consider the two possible cases:

| • | 1 | 0 | |||

|---|---|---|---|---|---|

| 0 |

|

1 |

|

| • | 0 |

|

1 |

|

|

|---|---|---|---|---|---|

| 1 | 0 |

Chapter 3 <8>

| R | N1 | Q | |

|---|---|---|---|

| S | N2 | Q |

|---|

Chapter 3 <9>

•S = 0, R = 1

•S = 0, R = 0

|

R |

|

N1 | 1 | |

|---|---|---|---|---|---|

| S | N2 | 0 |

|

Chapter 3 <11>

| R | N1 | 1 |

|

||

|---|---|---|---|---|---|

|

|||||

| S | N2 | 0 |

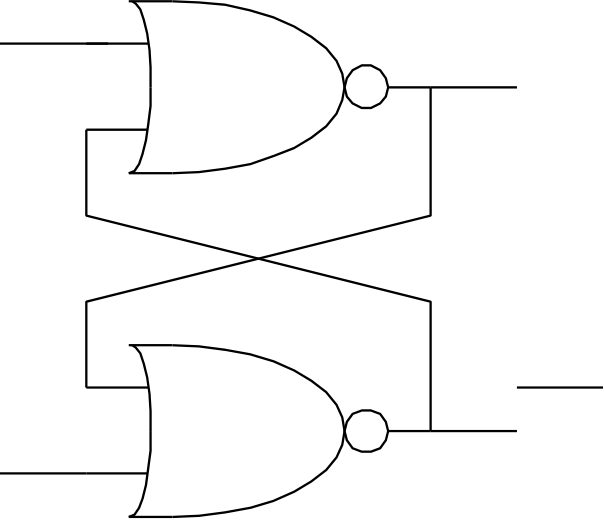

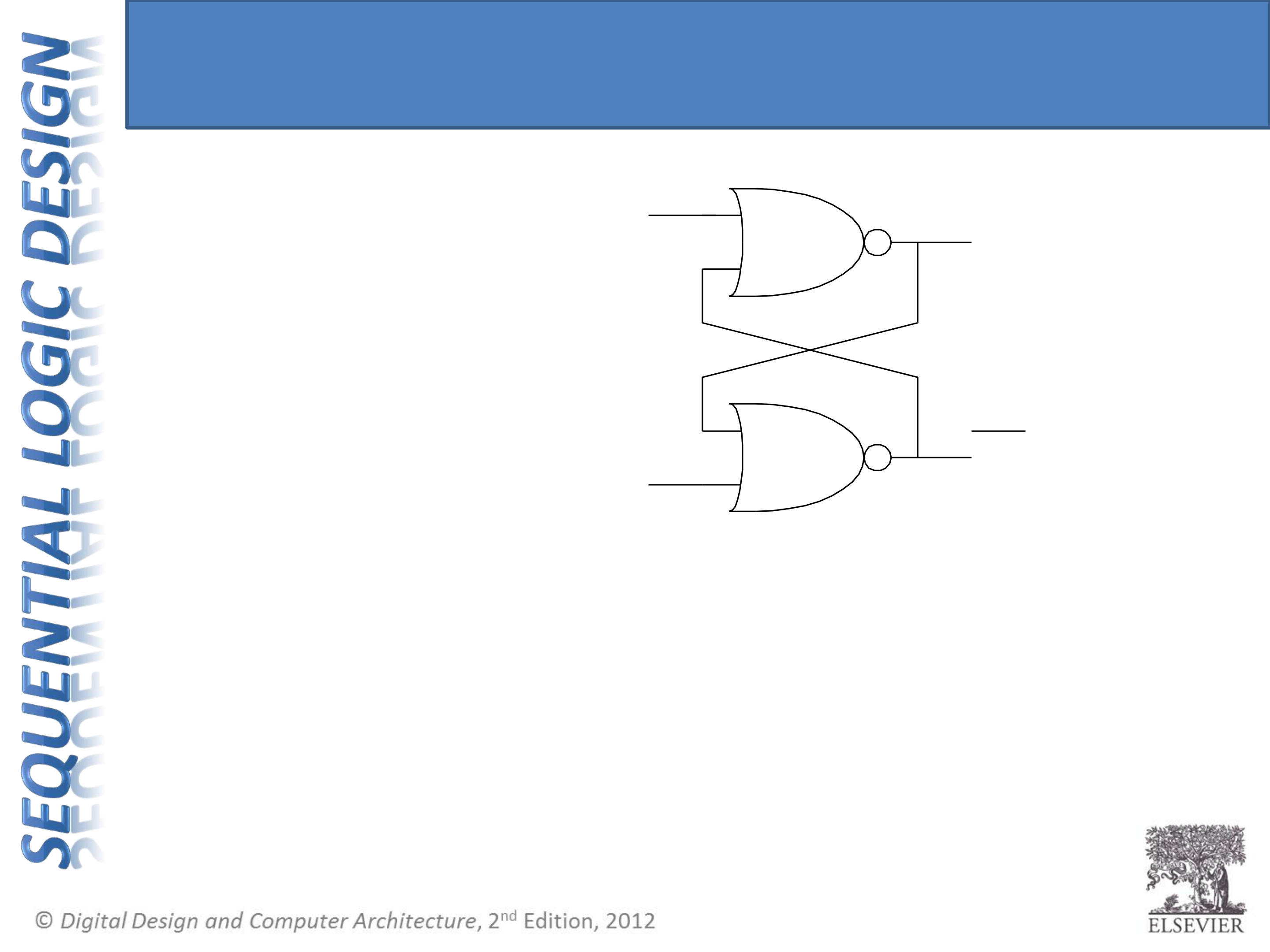

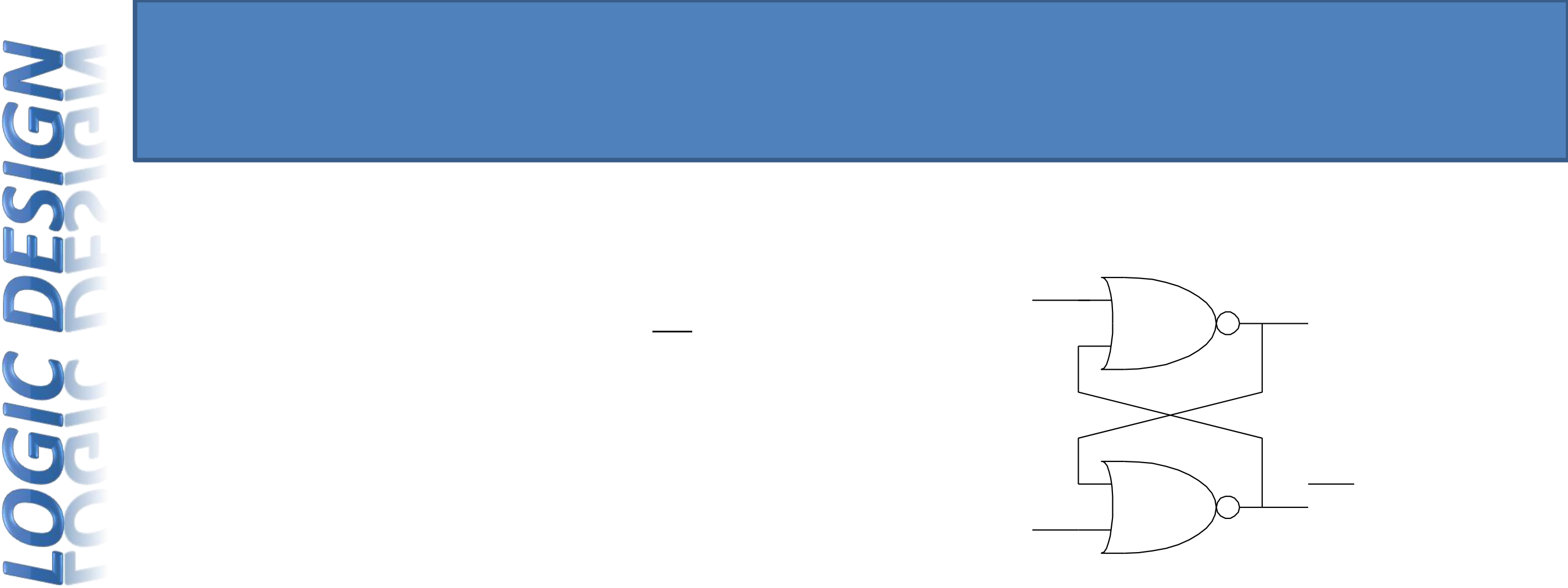

SR Latch Analysis• S = 1, R = 0:

then Q = 1 and Q = 0

| R | N1 | 0 | |||

|---|---|---|---|---|---|

|

| S |

|

N2 | 1 |

|---|

• S = 1, R = 0:

then Q = 1 and Q = 0 Set the output• S = 0, R = 1:

then Q = 0 and Q = 1 Reset the output

| Qprev= 0 |

|

|||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| then Q = Qprev | R |

|

N1 | 0 | R | 0 | N1 | 1 | ||

| S | N2 | S | 0 | N2 |

|

Chapter 3 <15>

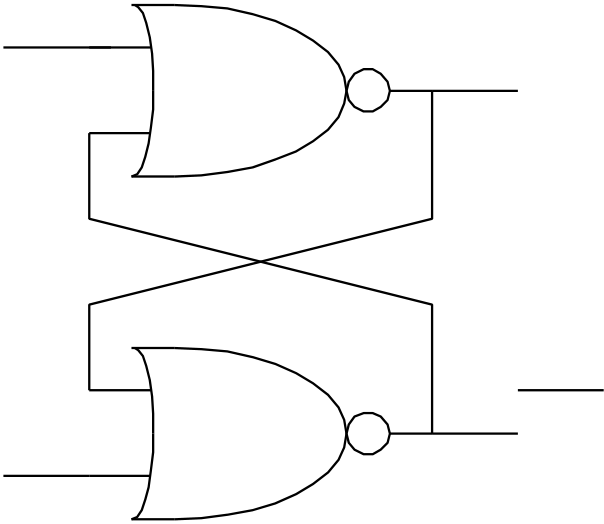

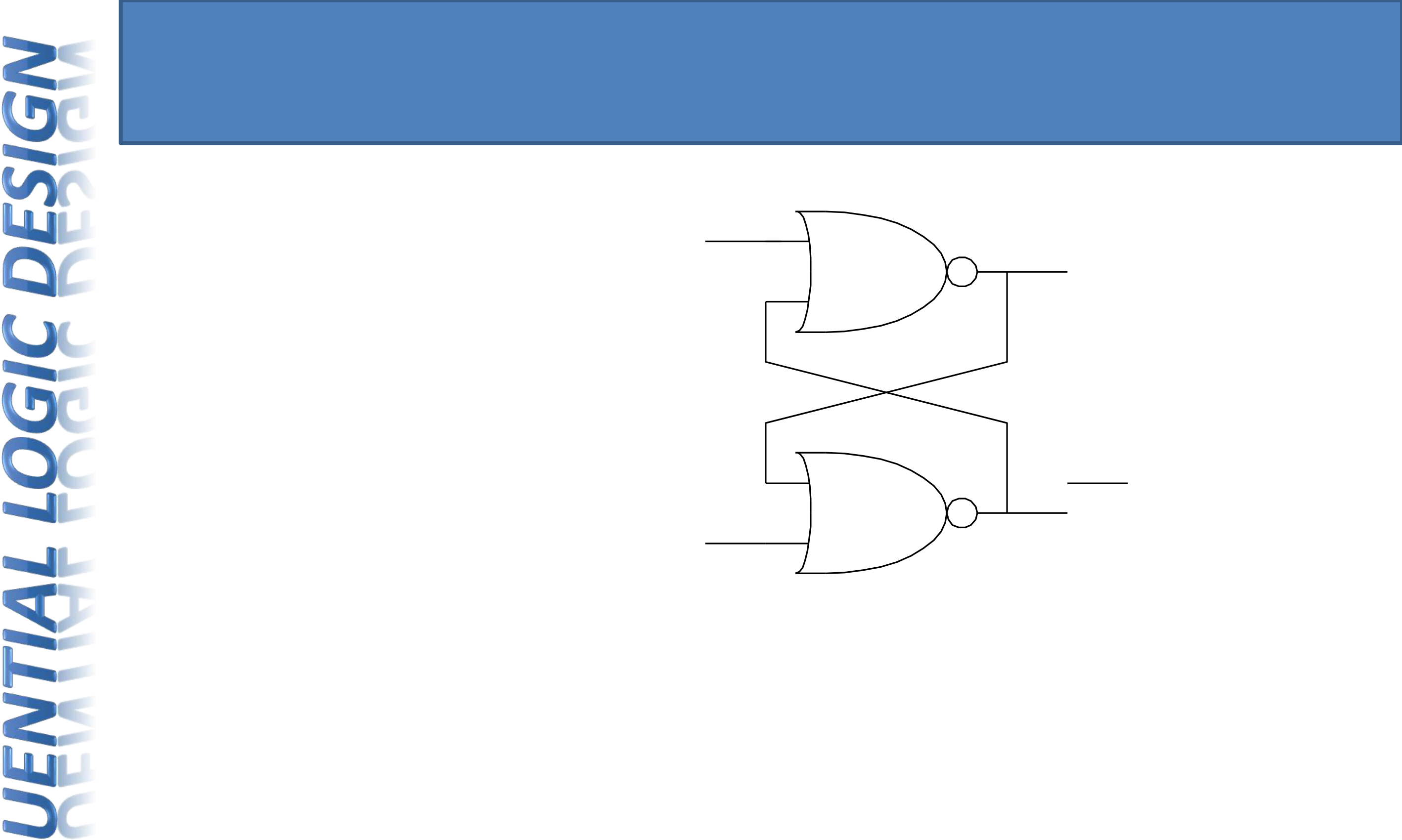

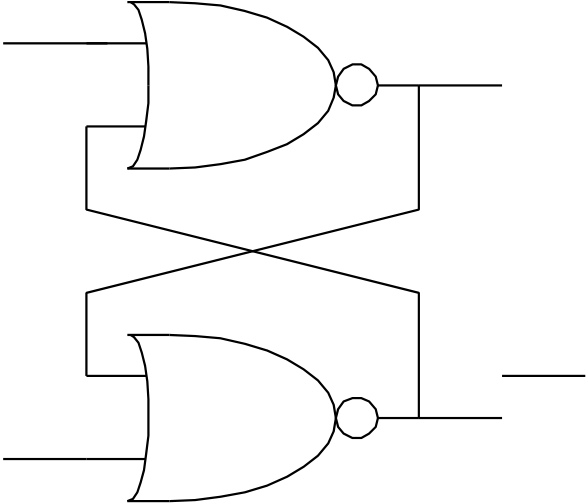

• S = 0, R = 0:

then Q = Qprev

|

R | N1 | 0 | ||

|---|---|---|---|---|---|

| S |

|

N2 | 0 |

|

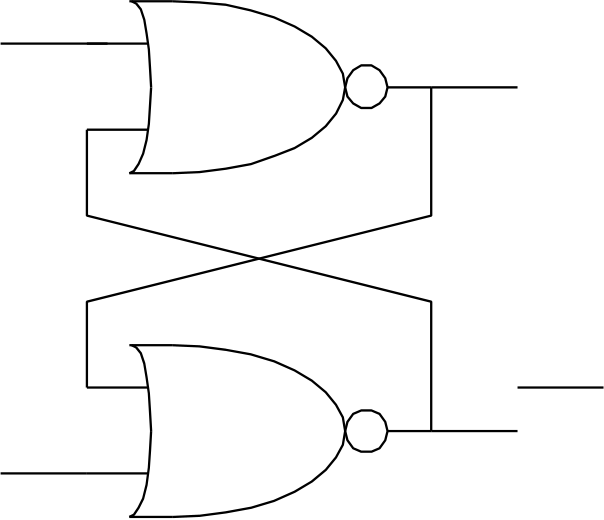

Chapter 3 <18>

|

|---|

| R | 0 | Qprev= 0 | 0 | R | 0 | Q | |||

|---|---|---|---|---|---|---|---|---|---|

| then Q = Qprev | N1 | N1 | |||||||

|

|||||||||

| S | 0 | N2 |

|

S | 0 | N2 | Q |

|

|---|