Calculate the maximum input power

|

|

||

|---|---|---|---|

| EXAMPLE 16.10 |

|

||

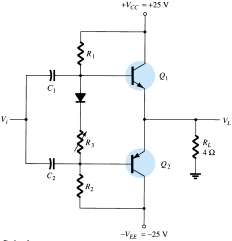

| Figure 16.19 | |||

Vi(p) � �2� Vi (rms) � �2� (12 V) � 16.97 V � 17 V

Since the resulting voltage across the load is ideally the same as the input signal (the

Po(ac) � �2 R� � �

L 2 ( 4

� � 36.125 W

L

p) 14

7� � 4.25 A

| Chapter 16 | � � � 2.71 A 5 A) |

|

|---|---|---|

| PL |

|---|

PQ � �P 2 2Q� � �Pi �

|

|---|

P .7 2� � 100% � 53.3% 5 5

|

|

|---|---|

| EXAMPLE 16.11 |

�

VR

� � �

2

� ) )

2[Note that the maximum efficiency is achieved:]

P2Q � Pi � Po � 99.47 W � 78.125 W � 21.3 W

|

EXAMPLE 16.12 |

|---|

2R

� � �

2L

2VL � 0.636VL(p) � 0.636(25 V) � 15.9 V

(Notice that at VL � 15.9 V the circuit required the output transistors to dissipate 31.66 W, while at VL � 25 V they only had to dissipate 21.3 W.)

| 16.5 | 703 |

|---|