Andi and immediate src src dstsll

MIPS registers

|

assembly name | |

|---|---|---|

MIPS insruction formats

Instruction “add” belongs to the R-type format.

| 6 | 5 |

|

5 |

|

|---|---|---|---|---|

| 6 | 5 |

|

5 | 6 |

|---|

The “function” field is an extension of the opcode, and

| 6 | 5 |

|

|

|

|||

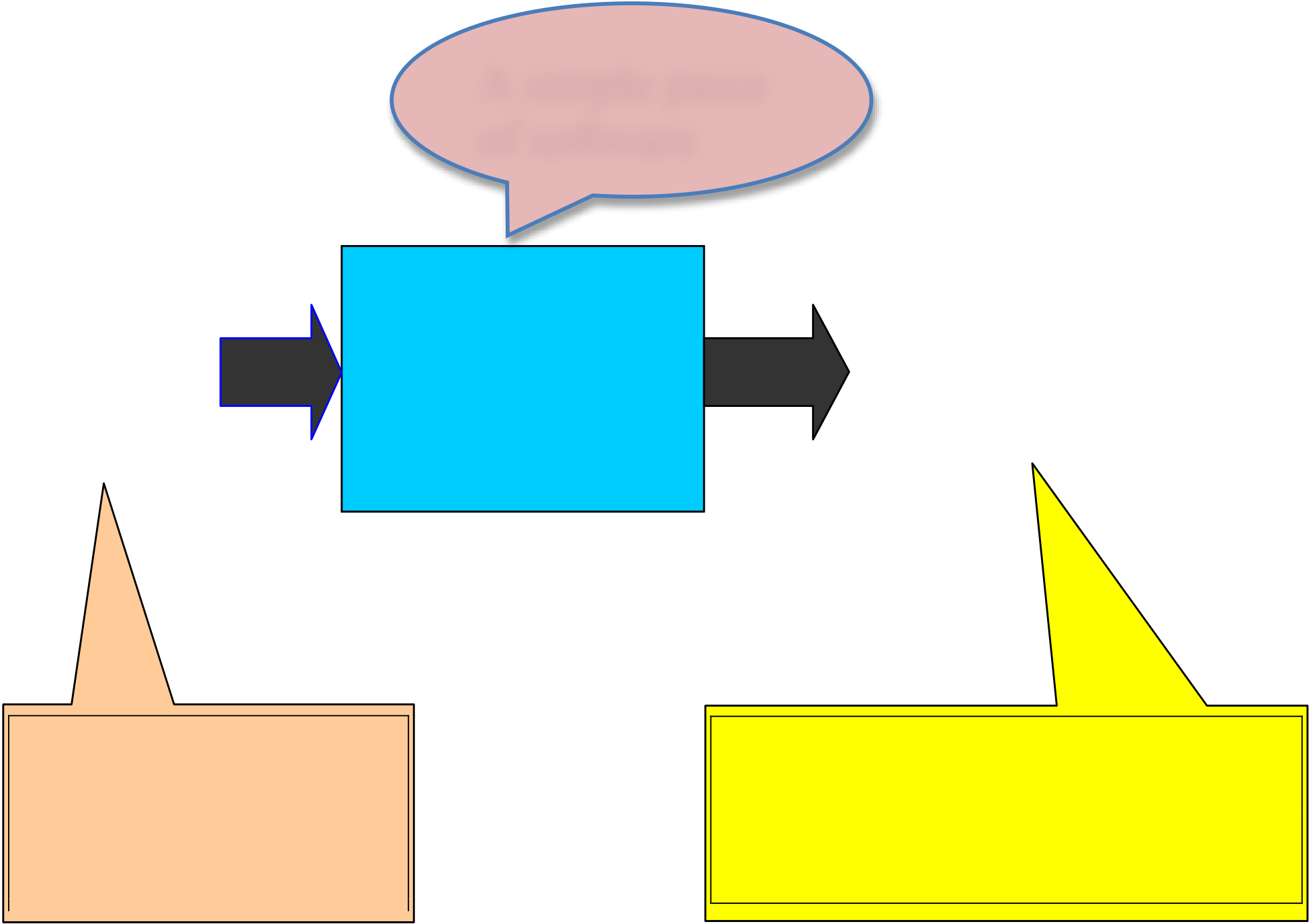

lw $t0, 32($s3)

| 6 | 5 | 16 |

|---|

| 0 |

|

REGISTERS | |

|---|---|---|---|

| 0 | |||

| 4 | |||

| 8 | |||

| 12 | |||

| 16 | |||

|

|||

| 20 | |||

| 24 | |||

| 28 | |||

| 32 |

|

||

(LW) LoadWord destination, offset($base register)

lw t0, 32($s3)

add $s1, $s2, $t0Example

move $t0, $t1 # $t0 ← $t1 The assembler will translate it to add$t0, $zer0, $t1

We will see more of these soon.Think about these

Q4. How will you load a constant (say 5) into a register?

(Need the immediate mode instructions, likeaddi)

hexadecimal

means “load the 32-bit constant into register $s0.”

Shift left (logical) sll

Shift right (logical) srl

(s0 = $16, t2 = $10)

| 0 |

|

16 | 4 |

|---|

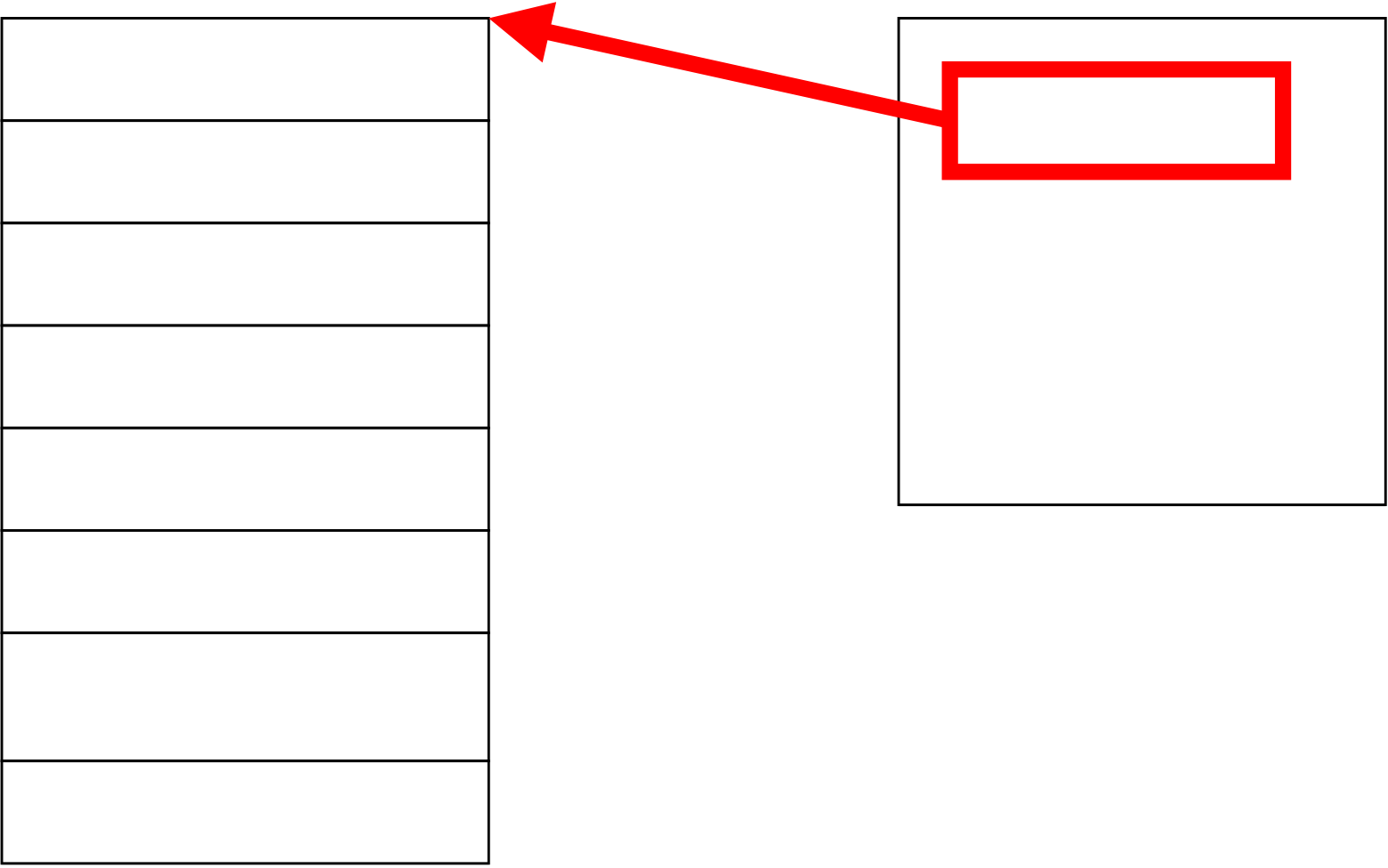

andi $t2, $s0, 1

This uses I-type format (why?):

| 8 | 16 | 1 |

|---|

Now we have to test if $t2 = 1 or 0

Use bne = branch-nor-equal, beq = branch-equal, and j = jump

|

||

|---|---|---|

|

||

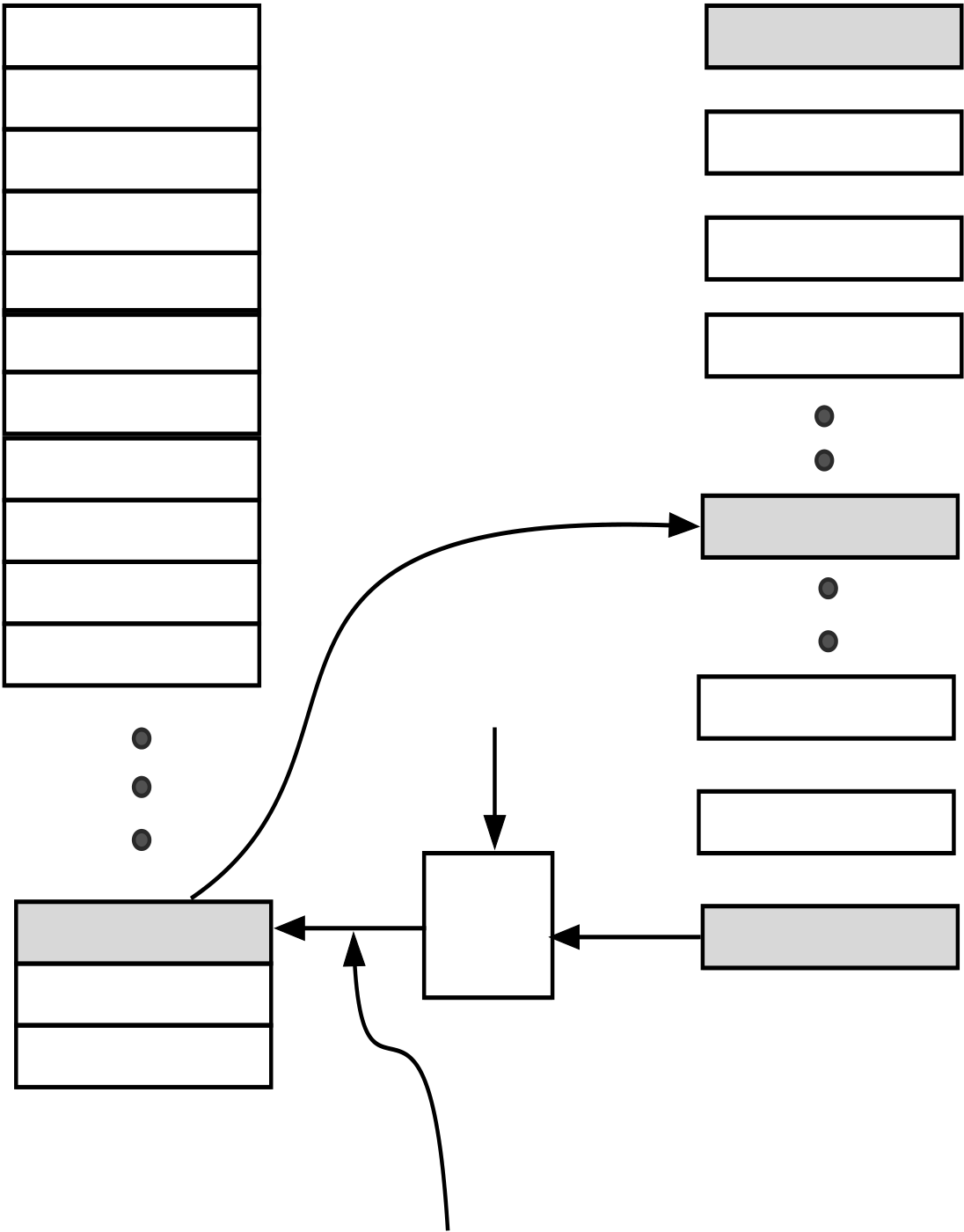

data

MEMORY

Let $s6 store the base of the array A. Each element of A

is a 32-bit word.

Anatomy of a MIPS assembly language program running on the MARS simulator

|

|---|

move $t0, $v0

add $t1, $t0, $t0 sw $t1, res($0)# move the value to $t0 # multiply by 2

# store result in memory